lain D. Craig

# Formal Refinement for Operating System Kernels

Formal Refinement for Operating System Kernels

Iain D. Craig

# Formal Refinement for Operating System Kernels

Iain Craig, MA, PhD, FBCF, CITP

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library

Library of Congress Control Number: 2007931774

ISBN 978-1-84628-966-8 e-ISBN 978-1-84628-967-5

© Springer-Verlag London Limited 2007

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Printed on acid-free paper.

$9\ 8\ 7\ 6\ 5\ 4\ 3\ 2\ 1$

springer.com

To my Father at 75

# Preface

This book was written as a companion to my book on modelling operating system kernels. It is intended to demonstrate that the formal derivation of kernels is possible (and, actually, quite easy, or so I have found *thus far*).

It is important for the reader to understand that the refinements contained in this book are not the only ones I have performed of microkernels. To date, I have refined four microkernels down to executable code and have now produced a kit of formally specified components that can be composed to form kernels. The first kernel included in this book is just one example of this work. The second kernel, the Separation Kernel, is new and was partly constructed out of the kit of parts (and the reader will see reuse in its specification and refinement) and was included for specific reasons that will become clear anon. Both kernels took less than three months' working time to produce (the actual time is rather hard to calculate because of frequent interruptions). Previous experience in refining kernels also paid off in the sense that there was little revision involved in their specification or refinement; the usual process of yo-yoing between levels of the derivation was absent. This appears to be an inevitable consequence of experience.

The time factor has been important in the production of the various kernels that I have derived. The micro kernel helps in no little way by imposing the rule that the kernel should be as small as possible. This is not to say that I would not be interested or willing to refine a kernel such as the second one I modelled in [4]. Such an exercise would be extremely interesting and one I would very much like to undertake; however, it would require time (and I am quite willing to put it in) and would require financial support. In today's climate, one would probably also have to ask what the point of such an exercise would be.

It is necessary to position this book. Mainly, I believe it to be an essay in formal methods software engineering and in operating systems. It can be argued that this book is a contribution to refinement, in particular, to refinement *in the large*. There is nothing in the literature on the scale of the refinements that are the subject of this book, as far as I am aware. The Separation Kernel was included for specific reasons. First, there is at least one document from the US National Security Agency (NSA) recommending the Separation Kernel as the cryptographic kernel *par excellence*. In their documents, the NSA also states that the formal specification of a Separation Kernel would be highly desirable. Having looked at the various documents, the original paper by Rushby [11] in particular, the structure and functioning of the Separation Kernel appeared to be fairly simple. This would appear to have been one of the goals that Rushby had in mind when defining the architecture in the first place—it is another good example of how simplicity wins every time (Less *is* more.) As a result, I wondered what a specification would look like. What I found was what I expected. The result was quite easy to specify and to refine.

The reader will observe that there is little or nothing about bootstrapping or hardware-specific initialisation. This is because we do not consider these matters to be part of the kernel; they belong to the *environment* within which the kernel executes.

I think it necessary to make a couple of observations about the refinement itself. In the Z literature, two kinds of refinement are described: one relational, one functional. The relational refinement is the worst-case scenario. The functional refinement is, in my experience, the usual case. Indeed, in more than twenty years' experience refining specifications, I have found that the relationship between the abstract and concrete statements is almost always an identity. This experience is not restricted to kernels (of course) for a great deal of the code I have produced during that time has had at least some formally specified component (usually the components that are the hardest to understand). The code has included virtual machines and parts of compilers, so it is quite varied. For this reason, the fact that the abstraction relations in this book are identities does not cause me any concern. (Steve Schumann reports in a private communication the same experience.) I decided that proofs, which are strictly unnecessary when using a functional abstraction relation, should be included in the book. This was to show how they enter the refinement process and to show that they are relatively simple (given the prevalence of identity relationships, proofs of similar complexity are to be expected and that is a level of complexity that can easily be handled). Furthermore, I wanted to counter the claims that either the proofs could not be done or that they were too complicated; neither is the case. In the case of the Separation Kernel, a number of proofs are omitted (this was also for the reason that space was getting short and devoting much more space to such a simple system did not appear warranted). This is particularly the case with operations defined over conjunctions of state spaces. The proofs and preconditions of the components are given, as are the abstraction relations, so the production of the required proofs is a straightforward matter and can be produced in a relatively short period. In each case, the compound operation was checked against the components and short (i.e., outline or sketch) proofs produced as a safety device.

The purely textual parts of this book were written using voice-input software because my daily typing time was severely restricted on medical advice. Using voice-input software for the first time was an interesting and sometimes frustrating experience. The frustrations were mostly due to my being so used to typing and I found that having to *speak* rather than compose on the keyboard sometimes confusingly difficult. In particular, initially, I found it quite hard to navigate back and forth using just voice commands. (It led to the occasional and unwanted inclusion of expletives in the text and I hope that I have removed them all!) With greater experience, it turned out to be an effective method for producing text. It is worth trying!

#### A Note on Interrupts

When I started out, it was conventional wisdom that interrupts should be disabled for as short a period as possible. The reader will note that the space between disabling and enabling interrupts in the specifications and refinements that follow can be rather large. In some case (e.g., the interface routines at the end of Chapter 3), the reason for this is that I wanted to emphasise the fact that interrupts should be disabled for some part of the operation (for reasons that will become clear in a second, without necessarily being forced into saying *which* parts). Some processors have pipelines that might affect the exact time at which the interrupt operation is performed; this cannot be taken into account until the processor is known, so the safe option was chosen. In addition, the period during which interrupts are disabled can be extended when the desired response time of the system is known (here, we have no such knowledge). In such a case, the interrupt operations can be moved using the distributive law  $(p \lor (q \land r) \Leftrightarrow (p \land q) \lor (p \land r))$  and the idempotent laws  $(p \land p \Leftrightarrow p$  and  $p \lor p \Leftrightarrow p)$ . In the other cases, the change to the interrupt flag (or whatever mechanism is used on the implementation platform) might have some interaction with another part of the system (e.g., on the IA32, if the *INT* bit in the *EFLAGS* register is not the same value as the processor interrupt flag, the system will crash); again, without knowing the exact hardware, precise location of the interrupt operations impossible.

#### Acknowledgements

First of all, I would like to thank Beverley Ford for agreeing to publish this book. Thanks are due in equal measure to Helen Desmond for making the process of producing this book as painless as possible. They have jointly performed the proof and copy editing stages of the test in order to expedite its publication. I would like to thank Steve Schuman for reading the manuscript while it was in sketch and in a more developed form and for a number of extremely interesting discussions on the refinement process (any errors are, naturally, my own fault). Considerable thanks are due to my brother, Adam. Once again, he drew the figures for me; in addition, he patiently typed those

#### x Preface

parts from my dictation that could not easily be done using voice-input software. Without his dedicated effort, the text of this book could not have been completed. As for the others who have helped (the regulars), as always, I offer my thanks.

Iain Craig North Warwickshire April, 2007

# Contents

| 1        | Intr                    | oducti  | ion                           | 1 |

|----------|-------------------------|---------|-------------------------------|---|

|          | 1.1                     | Reason  | ns for Selecting the Examples | 3 |

|          | 1.2                     | Refine  | ment Method                   | 7 |

|          | 1.3                     | Code 1  | Production                    | 9 |

|          | 1.4                     | Organ   | isation of this Book 10       | 0 |

|          | 1.5                     | Relati  | onship to Other Work 10       | 0 |

| <b>2</b> | The                     | e Simp  | le Kernel's Organisation 1    | 1 |

| 3        | $\mathbf{A} \mathbf{S}$ | imple   | Kernel                        | 9 |

|          | 3.1                     | Types   |                               | 9 |

|          | 3.2                     |         | vare                          | 3 |

|          | 3.3                     | The P   | rocess Table                  | 3 |

|          |                         | 3.3.1   | Top Level                     | 3 |

|          |                         | 3.3.2   | Refinement One                | 4 |

|          |                         | 3.3.3   | Refinement Two 44             | 4 |

|          | 3.4                     | Proces  | ss Queue                      | 6 |

|          |                         | 3.4.1   | Top Level                     | 6 |

|          |                         | 3.4.2   | Refinement One 59             | 9 |

|          |                         | 3.4.3   | Refinement Two                | 5 |

|          | 3.5                     | Priorit | ty Queue                      | 0 |

|          |                         | 3.5.1   | Top Level                     | 0 |

|          |                         | 3.5.2   | Refinement One                | 8 |

|          |                         | 3.5.3   | Refinement Two                | 1 |

|          | 3.6                     | The Se  | cheduler                      | 0 |

|          |                         | 3.6.1   | Top Level                     | 0 |

|          |                         | 3.6.2   | Refinement One                | 5 |

|          |                         | 3.6.3   | Refinement Two                | 3 |

|          | 3.7                     | Semap   | bhores                        | 9 |

|          |                         | 3.7.1   | Top Level                     | 0 |

|          |                         | 3.7.2   | Refinement                    | 6 |

|          | 3.8  | Semaphore Table                                            | 6        |

|----------|------|------------------------------------------------------------|----------|

|          |      | 3.8.1 Top Level                                            | <b>6</b> |

|          |      | 3.8.2 Refinement One                                       | 0        |

|          |      | 3.8.3 Refinement One–Again                                 | 3        |

|          | 3.9  | Synchronous Messages                                       | 1        |

|          |      | 3.9.1 Preliminaries                                        | 2        |

|          |      | 3.9.2 Top Level                                            | 3        |

|          |      | 3.9.3 Refinement One                                       | 5        |

|          |      | 3.9.4 Refinement Two                                       | 8        |

|          | 3.10 | The Clock                                                  | 8        |

|          |      | Sleepers                                                   |          |

|          | -    | 3.11.1 Top Level                                           |          |

|          |      | 3.11.2 Refinement One                                      |          |

|          |      | 3.11.3 Refiment Two                                        |          |

|          | 3.12 | User Interface                                             |          |

|          | 0.1- | 3.12.1 System Initialisation                               |          |

|          |      | 3.12.2 Process Creation                                    |          |

|          |      | 3.12.3 Process Management                                  |          |

|          |      | 3.12.4 Inter-process Communication and Synchronisation 198 |          |

|          |      | 3.12.5 Clock Operations and the Clock ISR                  |          |

|          |      | 3.12.6 Final Remarks                                       |          |

|          |      |                                                            | 2        |

| 4        | The  | Separation Kernel                                          | 3        |

|          | 4.1  | Basic Architecture                                         |          |

|          | 4.2  | Extending the Architecture                                 | 5        |

|          | 4.3  | Summary                                                    |          |

|          | 4.4  | An Overview of the Formal Specification                    |          |

|          |      | -                                                          |          |

| <b>5</b> | A S  | eparation Kernel                                           |          |

|          | 5.1  | Basic Types                                                |          |

|          | 5.2  | Hardware Issues                                            |          |

|          | 5.3  | Security Exits and Return Values                           |          |

|          | 5.4  | The Process Table                                          |          |

|          |      | 5.4.1 Top Level                                            | 0        |

|          |      | 5.4.2 Refinement One                                       | 3        |

|          |      | 5.4.3 Refinement Two                                       | 7        |

|          | 5.5  | Process Queues                                             | 9        |

|          |      | 5.5.1 Top Level                                            | 9        |

|          |      | 5.5.2 Refinement                                           | 2        |

|          | 5.6  | The Scheduler                                              | 2        |

|          | 5.7  | Storage Pools                                              | 1        |

|          |      | 5.7.1 Top Level                                            | 2        |

|          |      | 5.7.2 Refinement One                                       |          |

|          | 5.8  | Raw Storage                                                |          |

|          |      | 5.8.1 Top level                                            |          |

|          |      |                                                            |          |

|      |      | 5.8.2      | Message Buffering          |

|------|------|------------|----------------------------|

|      | 5.9  | Messag     | ge Queues                  |

|      |      | 5.9.1      | Top Level                  |

|      |      | 5.9.2      | Refinement One             |

|      | 5.10 | Kernel     | Interface – User Processes |

|      |      | 5.10.1     | Auxilliary Operations      |

|      |      | 5.10.2     | Initialisation             |

|      |      | 5.10.3     | Process Management         |

|      |      | 5.10.4     | Message Passing            |

|      | 5.11 | Device     | s—Trusted Code             |

|      |      | 5.11.1     | Device replies             |

|      |      | 5.11.2     | Device numbers             |

|      |      | 5.11.3     | Device process creation    |

|      | 5.12 | Proces     | s Interface to the Kernel  |

|      | 5.13 | Final 7    | Γhoughts                   |

| 6    | Clos | ing Tl     | houghts                    |

| Ref  | eren | <b>ces</b> |                            |

| List | of I | Definit    | ions                       |

# List of Figures

| 1.1 | The NSA cryptographic architecture              | 6 |

|-----|-------------------------------------------------|---|

| 2.1 | Organisation of the simple kernel 1             | 5 |

|     | Devices and interfaces in the Separation Kernel |   |

# Introduction

This book is a follow-up to our earlier one on the modelling of operating system kernels [4]. The aim of that book was to argue that formal specification of kernels was possible in the sense that formal modelling could be undertaken and then followed by a specification, a design and then refinement to running code. The first part of this was the subject of [4]. This book is concerned entirely with the specification, design and refinement to executable code of two operating system kernels. One kernel is of the kind found in small systems, while the other is intended for use in cryptographic and other secure systems. The book does not contain reasoning about models and concentrates on refinement. The refinements are from abstract or high-level specifications to a level at which programming language code can be immediately derived by obvious translation from the last stage of the refinement process.

In [4], it was our aim to show that detailed models were useful. This allows designers to identify properties of their designs without the need to construct a system. This could well have economic advantages and might spark new and necessary work in the general area of operating systems. It was also argued in that book that the *post hoc* verification of systems, particularly critical systems and components such as kernels, was not a good solution to the problem of reliability; instead, we argued that a synthetic method was superior.

The main purpose of the book is to demonstrate that the refinement of formal specifications of (micro) kernels is possible and, moreover, quite tractable. This should be obvious, given the fact that it is possible to model a (micro) kernel formally. The refinement is a process of documentation, as well as proof and justification, so it is worthwhile to record it, thus adding weight to the argument at the start of [4].

A secondary purpose is to give examples of refinements that are larger than those we have found in the literature. There are issues raised by the refinement process that are never considered in the standard literature:

• How many refinements should complex operations receive?

#### 2 1 Introduction

- When should implicit preconditions be used?

- When is it worth relying on the properties of functional abstraction relations?

Some might now argue that this is not a complete specification and refinement because we have not included device drivers and low-level deviceinterface code. Some might even go as far as to claim that this is not possible because, for example, it involves bitmasks; it also requires processes to wait for flags to change state. It is our opinion that the formal specification of such things is possible; this opinion is based upon experience with small examples and with the specification of low-level operations (for example, the bitmap that is used as the basis for the semaphore table in the first refinement below; we also specified some generic device-handlers while writing [4] but they had to be omitted for reasons of time and space).

In any case, at this point, we cannot specify the actual pieces of hardware that might be controlled by this book's systems. For this reason, we have to be as generic as possible, so we have concentrated on the specification of portable systems. This does mean that we have ignored low-level issues. On the contrary, we felt it essential that context switches and other essential kernel operations should be included in the specification. The approach we have taken is that the hardware and instruction set is a given and cannot be further refined. One aim of the work reported here was to reduce the assembly language programming to the level of triviality, thus making it possible to encapsulate the assembly language in a couple of operations<sup>1</sup>.

As can be seen from the specifications, interrupt-driven architectures are assumed, thus rendering the interface between the software and hardware specifications as small as possible. The context switch is thus reduced to a single instruction, one which raises an interrupt. The major part of the hardware specification is as generic as this. For the hardware architecture we have in mind, this is quite adequate and represents a reasonable specification of it; for other architectures (e.g., MIPS), it might be necessary to refine, perhaps, the high-level operations defined here.

By the publication of this book, we have shown that it is possible (and relatively easy) to specify small kernels and refine them to running code. What we have *not* done is try to specify a monolithic kernel such as the one used by Linux. One reason for this is that we do not care very much for the monolithic kernel for the reasons that it is too tempting just to add a feature to such a kernel on the grounds that there is nowhere else to put it (i.e., it is tempting not to solve a problem, just to throw things into the kernel); that is, the monolithic kernel does not require a clear separation of kernel versus non-kernel functionality. This lack of distinction has many implications for the performance of the resulting system. Instead, we prefer a smaller kernel that

$<sup>^{1}</sup>$  We write this as if assembly language were some kind of toxic material. There is no *a priori* reason why one cannot formally specify assembly-language programs, even though it is rarely done.

includes only those functions that are necessary. We prefer not to engage in further justification of our position; like many such debates, it is based upon a combination of technical and æsthetic factors.

#### 1.1 Reasons for Selecting the Examples

This book contains the specification and refinement of two kernels:

- 1. A small and simple kernel.

- 2. A microkernel for cryptographic and other secure applications. This kernel is an instance of the *Separation Kernel* concept of Rushby [11].

The first kernel is related to the  $\mu$ C/OS kernel of Labrosse [8], a kernel that has been employed in a number of real-time and embedded systems. The kernel specified and refined in this book is also a close relative of the first kernel model in our [4]<sup>2</sup>.

Another reviewer complained that the specification we gave in another paper was too simple to be of any use in real systems. We need to address this point because it could be levelled by the same reviewer of this work. The small kernel that is refined in this book is similar to  $\mu C/OS$  and other kernels for small systems. We have read the code of such systems, and also used them, over the period of a good many years. The kernels that we have looked at are not undergraduate exercises or simplified versions, they are *real* kernels that are used in *real* applications. The initial design of the small kernel is based upon this experience. It was intended that the level of functionality be such that it could be used with only minor modification (context switch and interrupt enable/disable operations) in a *real* application. The modifications expected require only minor modifications to the formal specification; the remainder would remain the same.

It is true that we have not included sophisticated real-time scheduling methods. However, the kernels that we have inspected and used do not contain them, either; to claim that we have an unrealistic, over-simplified system because it lacks some particular real-time scheduling algorithm appears unreasonable. It is also true that we have not included alarm timers. The reasons for this are that they are not always provided by the kernels that we have

<sup>&</sup>lt;sup>2</sup> A reviewer of a paper we wrote on this kernel strongly objected to the use of the adjective (they said "term") "real-time" in connection with this model. They claimed that the model could not be of a "real-time" system because it does not contain any temporal operators. There is a number of replies to this: (i) C and Ada are "real-time" programming languages but they do not contain temporal operators (and their formal semantics do not required them); (ii) there is a considerable number of small kernels similar to ours,  $\mu$ C/OS being one example, that are used in the development of "real-time" systems. We have read the descriptions, specifications and code of quite a few of these systems and have failed to locate a single temporal operator.

examined or used and that they are not particularly difficult to specify and, therefore, to refine to code using the formal method. If we extend the small kernel, asynchronous events such as alarms will constitute the first extension.

In brief, the kernel is composed of the following components.

- A process representation (the process table).

- A scheduler based on a priority queue.

- Semaphores in a global semaphore table.

- A simple synchronous message-passing system.

- A mechanism for putting processes to sleep for a specified period of time. (There is no alarm mechanism in this kernel, however).

- A set of initialisation and interface routines so that user-supplied code can call kernel operations (i.e., perform system calls).

User processes execute in the same address space as the kernel. To produce a working system, the code for user processes is linked to that of the kernel and the result bootstrapped somehow (this is considered outside of the specification, being, really, a processor-specific matter). Storage must be allocated by the user. This implies that they must define a memory map when designing their system.

It seemed appropriate to select this kernel as the first example refinement because

- It is a relatively simple example of a kernel. It contains no storage management, device drivers or Interrupt-Service Routines (ISRs).

- It makes few assumptions about the hardware upon which it runs. Indeed, it is quite portable; only a relatively few lines of code need be changed when porting to another processor.

On the other hand, the very simplicity of this first kernel is a problem *precisely* because it is processor-independent. In particular, there are no device drivers and ISRs to specify (other than the simple one for the clock). The specification and refinements employ a hardware model that is relatively general and portable; indeed, it can be employed on a number of processors. However, the interrupt mechanisms of processors vary considerably, so the specification included here is tailored to the Intel IA32 architecture<sup>3</sup>.

We could have included specific hardware devices into the specification and its refinement just to show that it is possible. This was not done because we want this kernel to be portable and the inclusion of a specific device might have suggested that we were not being portable. In addition, we had already encountered space problems with this book and the inclusion of the description of a hardware device, its interface and the specification of its ISR

<sup>&</sup>lt;sup>3</sup> The MIPS has also been considered and would have been used. However, we found problems with the GNU C compiler for the simulated MIPS that we intended to use.

and driver would have caused us to omit the Separation Kernel's specification, something we preferred not to do. We hope to specify a device's support software elsewhere in the near future.

The second example is the Separation Kernel introduced by Rushby in 1981 [11] for secure systems. The Separation Kernel derives its name from the fact that user processes are separated from each other both in space and in time. This implies that the address spaces of all user processes are disjoint and that the time during which one process executes can be identified as being different from that during which any other user process executes. The Separation Kernel is intended as a simulation of a distributed system. In a distributed system, in theory, all processes execute on their own processor, thus affording disjointness of address space. In addition, the execution of one process occurs on a processor during a particular time but does not affect the execution of other processes on other processors. Thus, one can say that process  $P_1$  executes on processor  $p_1$  during the period  $t_1 \ldots t_n$ , while process  $P_2$  executes on processor  $p_2$  during the period  $t_i \ldots t_m$ .

The problem is to translate this scheme to uniprocessor systems. This can be done by ensuring that all address spaces are disjoint, say by means of segmentation. Temporal separation can be had by ensuring that only one process executes at any point in time. Temporal separation is easy to arrange on a sequential processor (indeed, it is so obvious a property that it can be a little hard to explain convincingly).

The reasons for including the Separation Kernel are as follows:

- It is a little-known architecture and its specification and refinement are novel.

- It is a simple architecture and is, thus, easy to specify and refine in a few pages.

- It is an architecture that was explicitly defined for applications that should demand a formal approach to software development. Indeed, the US National Security Agency has stated [10] that the formal specification of Separation Kernels is highly desirable.

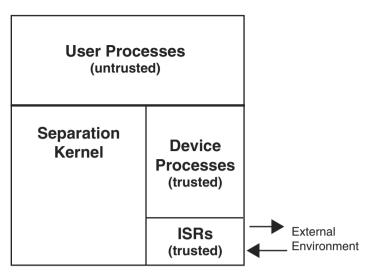

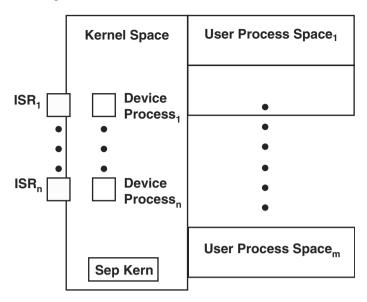

The specification and refinement in this book follow the recommendations of the National Security Agency's document [10]. The Separation Kernel proper is a microkernel that is formally specified. Upon the microkernel, there is a layer of so-called "trusted" code, principally device drivers and associated code. This trusted layer need not be formally specified but its specification, design and construction is carefully monitored so that it cannot engage in activities that would compromise the security of the system. Above this layer comes user-supplied code. This code is completely untrusted and can perform any activity and might be compromised in some way; although one might want this layer to be formally specified and tightly controlled, it is unlikely that it will be, at least in the near term. The overall architecture is depicted in Figure 1.1.

Fig. 1.1. The NSA cryptographic architecture.

The Separation Kernel itself is organised as follows (the reader will see that it is a simple structure):

- A process representation.

- A round-robin scheduler.

- Asynchronous inter-process message passing.

- Storage allocation mechanisms.

In addition, the specification includes:

- An interface for system calls from user processes.

- A collection of operations to support the construction of ISRs and device drivers.

These two last items are added so that the security of the system can be enhanced.

Our specification assumes that the processor upon which the microkernel executes supports segmentation. It was decided that virtual storage would not be included for the following reasons:

- Virtual storage requires some form of external store for page swapping. This would commit the specification to a particular hardware configuration, which was considered undesirable.

- It is possible in principle that external virtual storage can be attacked by malicious persons (e.g., corrupting or replacing pages). This was also considered undesirable.

It was, therefore, assumed that all user processes would reside in main storage and that they would be composed of two memory segments (the GNU C compiler generates two segments); they would be, in any case, memory resident. The kernel would also be memory resident. It would reside in segments that are disjoint from all others. Device drivers and ISRs are trusted code, so can be stored in the same segments as the kernel. This is more of an optimisation than anything else because it was considered that the time required to perform an address-space switch would not be tolerable for device-related code. Since this kind of code is trusted, it can be assumed that it will not interfere with the operations of the kernel (which is, in any case, an opaque chunk of code as far as they are concerned). The loading of user-process images into main store is something that we do not consider here (it is a matter that depends upon the hardware configuration); indeed, we have it in mind that the Separation Kernel would probably run on a co-processor. Finally, it was assumed that the processor would provide some mechanism for detecting illegal cross-segment references (segmentation errors) and that an ISR could be written to handle such references.

The assumptions of segmentation and cross-segment reference detection are reasonable. There are many processors supporting these features. The Intel IA32 and IA64 series of processors support them, for example.

For a full security kernel, it is necessary to write a formal security policy. This is an abstract model of the system that shows how violations of temporal and spatial separation are handled. This model has not been included in this book for the reason that it is not strictly relevant to the current task. However, readers should note that such a model for this specification is in the process of being documented and the relevant proofs are being undertaken.

#### 1.2 Refinement Method

The method adopted in this book follows the conventional approach as defined by Spivery [12] and Woodcock and Davies [13].

First, an abstract specification is created, then a refined version (the *concrete* version) is created; the two are then related by the definition of an *abstraction relation*. Proofs are then undertaken to show that concrete operations represent abstract ones correctly. The concept of correctness reduces to showing the following two properties. First, the states in which an abstract operation can start are also, modulo the abstraction relation, those states in which the concrete one can start. Second, it is shown that if the abstract operation terminates in a state, s, then the concrete operation terminates in a state,  $s_c$ , that is related to s by the abstraction relation. In addition, a theorem is proved that the initialisation of the two state spaces are equivalent.

Once this has been completed, what was the concrete version becomes the new abstract version. A new concrete representation and abstraction relation are defined and the process iterates. For the specifications in this book, some modules required no refinement, while others required two steps. In some cases, therefore, a state space was defined that does not require refinement; this is done when the state space consists of simple variables that are just updated by simple assignments. Example cases are the clock in the first refinement, parts of the scheduler in both refinements and the semaphore counter component in the first specification. In contrast, there are modules that required three refinement steps. It could be argued that two steps could be used instead. The reduction to two steps would, in our opinion, have made the refinement process less clear and clarity is an essential aspect of system design as well as documentation. The *PROCESSQUEUE* and *PRIOQUEUE* types both require two refinement steps: one from an abstract specification to an array-based representation and then to a representation based on the *next* attribute in the process table. The reader could try to refine the top-level specification to the one using *next*; it is certainly possible but, we consider, less clear than the three-step version.

In addition, the abstraction relation is an identity<sup>4</sup>. This makes proofs particularly simple. Indeed, because identity is a functional relation, the refinement process can be modified slightly, as outlined in [13]. Woodcock *et al.* show how the operation schemata can be calculated from the abstract specification and the abstraction relation. This has the implication that the proofs listed above need not be undertaken because they are guaranteed by the abstraction relation.

In this book, particularly in the first part, proofs are included; in the refinement of the separation kernel, some proofs are given but not others. In both exercises, the reader will see that the abstraction relations are all identities. We could have omitted the proofs in the refinement of the first kernel. We preferred not to do this for a number of reasons. First, we wanted to show how the full method operates on a scale somewhat larger than those usually found in the published literature. Second, we wanted to include proofs to counter the claim that they were either impossible, unintelligible or excessively complex; they are none of these and are all quite straightforward. In another of the kernel refinements that we have performed (but not published), some proofs did cause problems which were eventually resolved. Third, we also wanted to show how proofs are still possible even when working on conjoined state spaces. Fourth, undertaking a proof is a good way to gain a better understanding of the operation and it is also useful as a way of checking the abstract and concrete operation specifications as well as the abstraction relation. In another piece of work, we defined a concrete operation in a way that looked entirely sensible but it was found that it caused a revision of the abstraction relation which, it turned out, had not been properly thought out. Such errors or misconceptions should not be a cause for censure. Instead, they are valuable.

<sup>&</sup>lt;sup>4</sup> This is something that we have found in almost every refinement we have done over the last twenty-odd years.

In the refinement of the Separation Kernel, proofs of individual modules have been included. The two proofs associated with many of the complex operations (those defined over conjunctions of state spaces) are not included, even though they have been undertaken and recorded. One reason for this is space (the book would become excessively long); another is that too many obvious proofs become rather tedious and would put the reader off continuing. Finally, there is the reason that the proofs are not required because the abstraction relations are identities; the proofs of the components are given, so those of the complex operations can be derived in an obvious fashion.

Finally, as always, there is the matter of hardware. As in [4], we have treated the hardware as a given. For the purposes of refinement, this implies that it is a state space and set of operations that cannot be further refined. This does mean that the specification can appear a little low-level in places but, as usual, appropriate abstract operations are defined over the hardware state space (context switch, half context switch, raise interrupt and so on), so some measure of abstraction can be had. The approach adopted is, in any case, akin to that one must adopt when specifying software that interfaces to a pre-existant library or subsystem; the software external to the specification can only be treated as a given. In the case of system models, this implies that the properties of the external entity must be inferred. In the case of refinements, it implies that no further refinement can be undertaken (in any case, one has no control over pre-existant entities).

#### 1.3 Code Production

This book does not contain any code that can be executed. There are examples of the translation between final refinements and Dijkstra's Guarded Command Language [6]. These translations are included to show just how close to a programming notation the refinements reach.

There is no C or Ada. The complete code is not included. The reason for this is that there is no space.

We are, at the time of writing, translating the final refinements of the simple kernel into code so that it can be executed. The first refinement is has been translated to GNU C compiler. The target hardware is the Intel IA32 Pentium processor. The translation is a simple matter given the detail of the final refinement. Once translated into C, the result is tested and is, in this case, fairly exhaustive. It is pleasing to report that the code passed all of the tests. Testing, we believe, should be a confidence-building part of the method; we are making relatively exhaustive tests in this case because of the nature and size of the problem. All modules have passed their tests first time, so the refinement process can be argued to have worked. The low-level operations included in the specification are coded in assembly language; this is, again, a relatively simple activity. At the time of writing, the implementation has yet to be completed.

#### 1.4 Organisation of this Book

This book naturally falls into four main sections:

- 1. This introduction (Chapter 1).

- 2. The specification and formal refinement of a small kernel (Chapters 2 and 3).

- 3. The specification and formal refinement of a Separation Kernel (Chapters 4 and 5).

- 4. Concluding remarks (Chapter 6).

The two refinements are also accompanied by a short, informal, introduction that outlines the organisation of each kernel in high-level terms. The refinements are annotated in English; the main concern is to justify the decisions made in the face of alternatives.

#### 1.5 Relationship to Other Work

It has been pointed out that other workers have produced models of operating systems. This was a fact known to us when [4] was written. What made us continue with that book was the fact that it was intended that proofs of many properties, some obvious, some less so would be included in the book. Comparing what we wanted to do with the published literature, we found that published material either lacked proofs altogether or did not contain the range that we intended to produce (typically the former); we also wanted to work in a framework that was not based upon temporal logic.

As far as we are aware, there is nothing in the literature on the formal refinement of operating system kernel code from a formal specification.

In the case of verification, if one single bit in the code is altered, the entire system must be re-verified. Furthermore, verification often involves taking an informally specified object and reconstructing a formal specification from it. Unless the original designers are part of the exercise, it does not appear possible to determine whether the result of verification really does conform to the design. This must be true even when design documents are available for, as is often stated, a natural-language specification leaves a considerable amount unspecified because of our understanding of language. On the other hand, and this is another frequently made point, formal specification captures specifications unambiguously. The formal specification and refinement process requires that everything be captured in documents. It is clear that, should a single bit of a formally specified program be altered, the program no longer conforms to the specification. Unlike verification, it is possible, in this case, to determine whether the change is significant or not. It is also possible to propagate design decisions through a formal specification without requiring the production of code (by its very nature, verification depends upon the existence of code).

# The Simple Kernel's Organisation

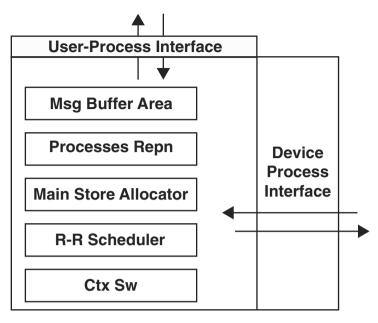

The purpose of this chapter is to describe in informal terms the organisation and purpose of the "simple" kernel that is specified in the remainder of this chapter.

As noted in Chapter 1, the kernel specified in this chapter is intended for use, actual or otherwise, as the kernel of embedded and simple real-time systems. The kernel is similar to Labrosse's  $\mu C/OS$  [8] and the first kernel modelled in [4]. This kernel was deliberately chosen as a link back to [4] and because we consider it important to demonstrate that this class of kernel can be formally specified and refined to working code.

In this kernel, each process has a unique identifier that is assigned to it by the kernel from a fixed set in a purely sequential fashion. The first process to be allocated is the *idle process*, the process that runs when no other processes are ready for execution; the second to be allocated will usually be the *initial process*, the process that creates all the other processes in the system (the model is *not* related to the one employed by Unix, it should be noted). Thereafter, the identifiers are allocated to processes in order of creation.

At present, each process has to make an explicit system call to obtain its identifier and there is no facility for determining, at runtime, the identifier of other processes (unless they, too, have determined their identity by means of the same system call). An obvious extension would be to make process identifiers available in a more usable way. Meanwhile, the mechanism specified here is workable.

The process representation is a set of mappings that are refined to vectors (one-dimensional arrays). The collection of these mappings is equivalent to the process table in other systems and we will refer to this collection of mappings as the *process table* or *PTAB* (this is the name of the state representation in the specification). The mappings are keyed by the identifier of the process and each mapping represents a different piece of information about the process.

In this kernel, the representation of processes is uniform in the sense that all processes are associated with the same kinds of information (in the other kernel specified in this book, there is a distinction imposed between different types of process). In this kernel, processes are represented by the following information:

- *Stack pointer*. This is a pointer to the top of the process' stack. It is used when performing a context switch.

- *Priority.* This is a small integer value. Small negative values represent high priorities, while small positive values represent low priorities. The default value is 0. The priority is used to sort the scheduler's *ready queue* and is also used to determine whether or not to cause a context switch.

- State. This is an enumeration type. The value associated with each process denotes the current state of the process. The state is used by the scheduler when determining whether a context switch can be performed. It is also used to document the process; an extension to the system is the inclusion of an operation that obtains the states of all the processes in the system (an operation similar to the Unix **ps** operation).

- *Incoming Message.* Processes can communicate using synchronous messages. This mapping is used to hold the latest message that has been sent to each process. When there is no message to be received or a message has just been read by its receiver, the value of the mapping is *nullmsg.*

- *Waking Time.* Processes can perform a system call that makes them wait for a specified period of time. The process specifies the duration of its sleeping time. The value stored in this mapping is the sum of the current time and the time at which the process should wake up. When a process wakes up, it is returned to the scheduler's ready queue and can be executed at some subsequent time.

In many kernels, processes are represented by structures or blocks of storage; the Linux kernel [2], on the other hand, employs an array-based representation similar to the one adopted here. A block/structure-based representation can be specified in Z and would use promotion to include the structure in the containing table. This approach separates the refinement of the structure from that of the table. The refinement process employed here combines the refinement of the mappings.

There are arguments for and against the benefits of these representations. As far as we are can see, the arguments balance out and what is left is personal preference. In other kernel specifications, we have adopted the other representation to good effect; in the end, though, we just like the mappingor vector-based implementation of the process table.

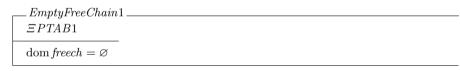

In addition, the process table contains a state variable, *used*. This contains the identifiers of those processes that have been allocated. If a process identifier is not in this set, it does not represent a process that currently exists in the system. This variable is refined to the *freechain*. The freechain is a chain of elements in a vector called *next*. If an element is in the freechain, it denotes a process that is not in the system; the identifier of the process is the index of the element in *next*.

The next major component is the scheduler. The scheduling régime is based on a simple priority queue with highest priority at the head. We refer to this queue as the *ready* queue. When a process is added to this queue, its priority is used to determine where it should be inserted.

The priority queue is first specified as a separate module, whose elements are in a variable called pq. For the specification of the scheduler proper, promotion is used so the refinement of the priority queue can proceed independently of that of the rest of the scheduler.

The priority queue is refined to a chain through the *next* PTAB map. This removes the need to allocate additional storage inside the kernel. The complexity of the chain operations is a little higher than those on a simple one-dimensional vector but it was employed here for the following reasons:

- It shows that such chaining can be handled formally.

- Chaining, as noted above, uses no more space in the kernel.

The scheduler proper contains three variables in addition to the ready queue. One variable contains the identifier of the *null process* so that it can be easily accessed when the scheduler determines that there is nothing to do.

The null process is included explicitly as a process for the following reasons:

- It can be removed in other versions of the system.

- Its behaviour can be altered from a completely null behaviour (an infinite loop with no body) to something else.

These modifications require trivial respecifications of the system.

The other variables contain the identifier of the process that is currently executing and that of the process that ran immediately before the current one. The identifier of the currently executing process is required by the scheduler when performing a rescheduler operation, as follows. A slightly simplified account of the scheduler's conditions for rescheduling are as follows. If a reschedule is to be performed and the following conditions are satisfied, the scheduler schedules another process and performs a context switch:

- There are processes in the ready queue.

- The priority of the current process is lower than that on the head of the ready queue.

- The state of the current process is not marked as *ready* or *running*.

If there are no processes in the ready queue, the idle process is run. If either of the other conditions is not satisfied, the current process is continued and no context switch is performed.

Keeping the current and previous process identifiers is also useful when performing the context switch because it allows the switching code to access process data. It is also useful when testing systems built using the kernel. In the current version, it allows the scheduler to access the stacks of the two processes.

The scheduler provides the following operations:

#### 14 2 The Simple Kernel's Organisation

- An operation to initialise the various data structures. This is called on system start-up.

- An operation to schedule the next process (*SchedNext*).

- An operation that suspends its caller and schedules the next process. If there are no other processes in the ready queue, the idle process is run. The operation forces a context switch.

Processes can synchronise using semaphores. The kernel contains a single table that holds all the semaphores that can be used by processes. The size of the table is a compile-time constant. It is organised as a bit map. The semaphores held in the table are *counting* semaphores; this is no restriction upon the semaphores' behaviour because the semaphore type contains an initialisation variable that can be set to 1 for binary semaphores.

Semaphores are defined as a separate type. Semaphore operations are promoted by the table type. There are three operations provided by semaphores:

- 1. Initialise.

- 2. Allocate a semaphore if possible (if not, an error is reported).

- 3. Free a semaphore<sup>1</sup>.

- 4. Signal (the V operation).

- 5. Wait (the P operation).

The refinement of the semaphore table to bit maps was performed in order to demonstrate that structures requiring "bit banging" can be specified formally<sup>2</sup>.

Semaphores are implemented using promotion. The semaphore proper contains a counter and a FIFO queue. The queue is defined as a separate type and its operations are promoted by the semaphore, thus simplifying the refinement. The FIFO is, like the priority queue, refined to a chain through the *next* map in the process table. In this case, chaining was considered essential. This is because there could be many semaphores in the system. Each semaphore contains its own, independent, FIFO queue. If the FIFO were implemented as a vector, this would mean allocation of a vector of suitable size for each semaphore. The scheme adopted here has the advantages that the space is allocated once and that each FIFO can be of arbitrary length.

Processes can also communicate by the synchronous exchange of messages. When a process is ready to receive a message, it executes a system primitive and enters the *psreceiving* state and is suspended. It remains in that state

<sup>&</sup>lt;sup>1</sup> No check on ownership is performed, so freeing someone else's semaphore is a neat way to cause trouble! In a more secure version, recording the ownership of resources would be a good idea.

<sup>&</sup>lt;sup>2</sup> In other work, we have also attempted the specification of the kinds of operations required, for example, in controlling hardware devices. Device controllers typically require bits to be set and unset by controlling software; they are often cited as a problem for the formal approach. After a little thought, we found that there is no such problem—provided, that is, one thinks clearly about it.

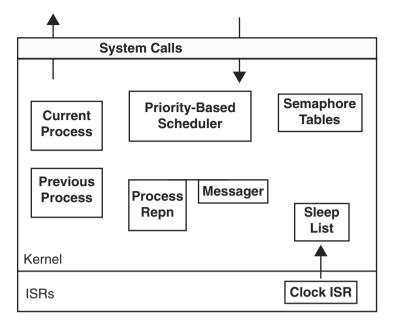

Fig. 2.1. Organisation of the simple kernel.

until another process sends a message to it. When the message is received, the receiver's state is set to *psready* and it is put back into the scheduler's ready queue. If a process sends a message to a process that is not blocked in the *psreceiving* state, the system reports the fact and the sender must try again (this rather crude approach could be hidden inside a library routine).

The organisation of this kernel is shown in Figure 2.1.

The interface to the system's facilities are made as simple and direct as possible so that the result is reasonably fast. In addition, the kernel assumes that the code implementing processes is linked with the kernel to form a single, loadable image. Storage is allocated by the programmer; the kernel, as it stands, does not contain any storage-allocation code. Storage can be allocated as data structures in C or assembly code or can be allocated as part of the linkage process.

The specification defines system calls for many of the operations mentioned above. Included in the calls are the following:

- Create process.

- Terminate. This operation is used when a process needs to terminate itself (it should be the last operation performed by all processes except the initial one). The operation works by killing the currently active process.

- Get process identifier.

- Send a synchronous message.

- Receive a synchronous message.

- Allocate a semaphore; an identifier is returned.

- Deallocate a semaphore. The identifier returned by the allocation operation is used to identify the semaphore to be freed.

- Wait. The *P* operation on a semaphore.

- Signal. The V operation on a semaphore.

- Sleep. This causes the suspension of the caller for the specified period of time. When the time has elapsed, the caller is resumed.

Each system call works as follows. It first disables interrupts, then performs the operation and finally re-enables interrupts. Disabling interrupts ensures that the operation is indivisible. Most of the operations are quite short, so interrupt disabling should not cause too many problems (this is not a kernel for hard real-time processing, in any case).

The specification includes the mechanism for making processes sleep. This is another case in which a high-level specification is refined to a chain through the *next* vector in the process table. When processes are not sleeping, their *waking time* value is 0; when they are sleeping, the *waking time* value is greater than 0. This provides a quick check that a process is not asleep.

To make the sleep mechanism work, the specification contains a clock. The clock is intended to be implemented as an *Interrupt Service Routine (ISR)* or *interrupt handler*.

The clock should work as follows. On every interrupt from the real hardware clock, the clock ISR increments a *tick* variable. If there are t ticks each second, when tick = t, the time in seconds since boot time is incremented by one, as is a second variable that records the number of ticks since boot time. If the number of seconds since boot is 0 mod 60, the minute counter is incremented by one; if the minute counter is 0 mod 60, the hour counter is incremented by one. In the current version, the actual clock time is not recorded (this could be included with relatively little work but could involve a hardware dependency).

If the clock used by the processor ticks at a rate such as once every 100msec, the above scheme can be used. Unfortunately, some processors do not have such accommodating clocks. The Intel IA32, for example, has a clock that has a cycle of something like 18.4MHz, a rate that is not all that help-ful for keeping the time. For the IA32, the clock ISR is activated on every clock interrupt, as usual. When activated, the ISR increments an activation counter. When the activation counter reaches a certain value, the *tick* counter is incremented, as above. The IA32 clock's rate is doubly awkward because it does not divide the second exactly, so either a little clock drift has to be tolerated or a correction must be made from time to time. In the specification here, drift is tolerated (it is an example, after all!)

Now, many readers will be wondering about the real hardware issues. In particular, how context switches are performed. Furthermore, nothing has been said about processor registers—the process context, in other words.

The answer is that we prefer to have as little as possible to do with the processor's low-level details! One reason for this is that it makes the kernel more portable (all the hardware-specific operations are firmly delineated). The low-level operations required are:

- Enable and disable interrupts. These operations are usually performed by one instruction each.

- A return from interrupt (*IRET*) is also required to terminate ISRs. This is also frequently implemented as one or two instructions (usually one but, on the MIPS, for example, interrupts must be re-enabled and the return has to be performed explicitly).

- A context switch. The scheme adopted in this specification is that the registers are stored on the top of the process stack. This has the advantage that there is no permanent store allocated in the process table for the register set; this also implies that it is not necessary, *a priori* to fix the number of registers in the process table.

- A "half-context switch". This is used to set up the initial process' registers when creating it. This operation pushes one value (0) onto the initial process' stack when it is created. The reason for this is explained immediately below.

The context-switching scheme is also a fairly standard one. When the scheduler requires a context switch, it raises an interrupt. This interrupt is handled by an ISR that pushes the outgoing process' registers onto its stack and then pops the incoming process' registers from the stack. The ISR then immediately executes an IRET instruction and the incoming process is switched in.

Because the incoming process has been suspended using an interrupt, it will have the registers needed by the IRET instruction on its stack immediately below its other registers. This is clearly impossible if the process has never been interrupted, as is the case with the initial process. In this case, the stack must be set up so that the processor finds all the information it requires. To do this, dummy values are pushed onto the stack when creating the initial process. The IRET instruction needs to have an address to which control should be returned. Usually, this is the address of the instruction that was interrupted. In the case of the initial process, the address has to be its entry point.

On an Intel IA32, the above scheme is extremely easy to implement. The hardware pushes the return address and the flags register onto the interrupted process' stack when an interrupt occurs. The **pushad** instruction pushes the general-purpose registers onto the stack and the **popad** instruction pops them back. If the kernel executes within a single address space (as this one does), there is no problem with the scheme outlined above (the Separation Kernel in Chapter 5 uses multiple address spaces, so another approach is required).

On a MIPS, the scheme outlined above can still be used. However, it is up to the implementer to push and pop the registers. In addition, the returnfrom-interrupt operation must be implemented as a macro. First, the interrupt flag is reset; next, the instruction pointer in force when the interrupt occurred must be fetched from a co-processor register and incremented by four (four bytes, i.e.) and stored in a register; finally, a jump-on-register instruction is executed, citing the register in which the old instruction pointer is stored.

Although a bit longer, the MIPS sequence is still comparatively simple. It is clear that it can be represented in Z with a little work. Because we are aiming our refinements and implementation at the IA32/64 (simply because we have them available), we have omitted a detailed specification of the contextswitching operation. A specification for the MIPS (or any other processor like it, for that matter) would include the specification of the registers and the operations required to implement the push and pop operations, as well as the return-from-interrupt operation. This is not difficult; indeed, we undertook it when examining a refinement of this kernel to the MIPS processor<sup>3</sup>.

With this general outline of the kernel and the refinement out of the way, it is possible to progress to the specification and refinement proper. Both top-level specification and the various refinements are accompanied by a commentary to aid the reader's understanding.

$<sup>^{3}</sup>$  We did this as an exercise in refining to a RISC machine to determine what the problems, if any, might be; as with the IA32/64, we were pleased to find that it was straightforward. Unfortunately, we do not have a MIPS or other RISC available so that we can run the result—perhaps, one day!

# A Simple Kernel

The first specification and refinement is of a small kernel of the type often used in embedded and real-time systems. The kernel resembles Labrosse's  $\mu C/OS$ [8] and the kernel of Chapter 3 of our [4].

The structure of the chapter is as follows. First, the types that are used throughout the specification and the refinement are defined.

Second, a specification of the hardware is given. This specification is at a relatively high level but could be refined to a lower one. The specification is aimed at an Intel IA32 implementation but should be sufficiently general to change to another architecture.

Third comes the specification and refinement of the kernel proper. This part occupies the vast majority of the chapter. Each major component is specified and then refined; this constitutes a section of the chapter. Refinements constitute a subsection and usually consist of the refined state space and operations followed by the abstraction relation; in some cases, where it seems more appropriate, the abstraction relation comes before the refined operations. The relevant proofs come at the end of each section. In a couple of cases, proofs are included within the statement of the refined operations.

#### 3.1 Types

In this section, the major types are defined. As noted above, the types defined here are used throughout the rest of this chapter.

First, the *PID* and *GPID* types are defined. These types are used to name processes. The *PID* type is a subrange type with range *minpid* to *maxpid*, while *GPID* extends *PID* by the addition of the *nullpid*. The *nullpid* is defined below and represents the null process. The *null* process should not be confused with the *idle* process; the former is intended to be a null reference, while the latter merely does nothing while it executes—it is executed when the processor has nothing to do. The *idle* process has a normal process identifier (an element of *PID*) and is allocated at system startup time.

$PID \stackrel{\frown}{=} minpid \dots maxpid$  $GPID \stackrel{\frown}{=} \{nullpid\} \cup PID$

$nullpid : \mathbb{N}$  $\forall p : PID \bullet$ p < nullpid

The null value is usually the least element or somewhere in the middle. However, in a implementation using C vectors, indexing is zero-based, so the natural choice of zero is not available. The actual choice of value for *nullpid* is, in any case, arbitrary; what must be ensured is that there is no way in which *nullpid* can be confused with a valid value.

The PSTATE type is defined next.

PSTATE ::= psterm

psrunning psready pswaitsema pssleeping pssending psreceiving

This type represents the state of processes. A process can be in exactly one state at any time. The names denote states:

- State *psterm* denotes the *terminated* state.

- State *psrunning* is the state of a process that is currently executing.

- State *psready* is the state of a process that is ready to execute but not yet executing.

- State *pswaitsema* is the state of a process that is waiting on a semaphore.

- State *pssleeping* is the state of a process that is in a sleeping state (i.e., is waiting for a timer to expire before it can resume execution).

- State *pssending* is the state of a process that is sending a message (this might involve the process being suspended before the message can be exchanged).

- State *psreceiving* is the state of a process that is ready to receive a message.

The next definitions concern process priorities. Priorities are defined in terms of the range *maxprio*...*minprio*, with smaller values denoting higher priorities.

$minprio, maxprio: \mathbb{Z}$

The type denoting process priorities is *PPRIO*.

$PPRIO == maxprio \dots minprio$

The type representing messages is, for simplicity, defined as atomic.

[MSG]

The MSG type includes a value denoting the null message:

nullmsg:MSG

It will be necessary to access components of elements of MSG. It is common, for checking purposes, to require access to the sender (msgsrc) and destination (msgdest) of a message; in addition, the msgsize function returns the size of a message

$\begin{array}{l} msgsrc: MSG \rightarrow PID \\ msgdest: MSG \rightarrow PID \\ msgsize: MSG \rightarrow \mathbb{N} \end{array}$

The WORD type denotes the contents of a word of storage.

[WORD]

Addresses in the store are represented by the ADDR type.

$ADDR == nulladdr \dots maxaddr$

Addresses are defined in terms of a range. The lower bound, nulladdr is address zero.

$\begin{array}{l} nulladdr: \mathbb{N} \\ maxaddr: \mathbb{N} \\ \hline \\ nulladdr = 0 \\ nulladdr < maxaddr \end{array}$

A representation is also required for time. This representation is called *TIME*. It is defined as a synonym for the naturals. Time can be assumed, for now, to start when the system is started.

$TIME == \mathbb{N}$

Finally, the *SYSERR* type is defined. This type defines the values of the error variable set by various system components. When all is well, the error variable is set to *sysok*; when an error has occurred, the variable is set to another value.

SYSERR ::= sysok | pdinuse | unusedpd | ptabfull

#### 22 3 A Simple Kernel

emptyqueue schedqfull schedqempty alreadyasleep toomanysleepers notallocsema nofreesemas procalreadyhasmsg destinationnotrcving badmsgdestination nomsg

The interpretation of the values are:

- Value *pdinuse* denotes the state in which a process descriptor (process identifier) is already in use;

- Value *unusedpd* denotes the state in which a reference has been made to a process descriptor that is not in use.

- Value *ptabfull* denotes the state in which no more process descriptors can be allocated.

- Value *emptyqueue* denotes the state in which a queue of processes is empty and an attempt to dequeue a process has taken place.

- Value *schedqfull* denotes the state in which the scheduler's ready queue is full.

- Value *schedqempty* denotes the state in which the scheduler's ready queue is empty.

- Vaue *alreadyasleep* denotes the state in which an attempt is made by a process to enter a sleep state but that process is already marked as being asleep.

- Value *toomanysleepers* denotes the state in which there are too many processes in the sleep list.

- Value *notallocsema* denotes the state in which an attempt has been made to access a semaphore that has not been allocated.

- Value *nofreesemas* denotes the state in which no more semaphores can be allocated.

- Value *procalreadyhasmsg* denotes the state in which a receiving process already has an incoming message but has not yet processed it (thereby freeing its incoming-message slot).

- Value *destinationnotrcving* denotes the state in which the intended destination of a message is not currently in the state to receive it. The sender should wait until later.

- Value *badmsgdestination* denotes the state in which the destination process of a message does not exist.

- Value *nomsg* denotes the state in which there is no message in the incoming-message slot when an attempt to receive a message is made.

This section concludes with the definition of three schemata that are used in generic error situations.

When all is well, the SysOk schema sets the error variable, serr!, to sysok.

| SysOk         |  |  |  |

|---------------|--|--|--|

| serr!: SYSERR |  |  |  |

| serr! = sysok |  |  |  |

The following operation tests *err* to determine whether it is *sysok*.

\_\_\_IsSysOk \_\_\_\_\_ err : SYSERR err = sysok

This operation is used to re-direct the value of *serr*!. It is intended that *terr*? should be renamed when using this schema.

\_\_\_ReturnSysError \_ terr? : SYSERR serr! : SYSERR serr! = terr?

#### 3.2 Hardware

The reader is warned that this section is heavily influenced by the Intel IA32/64 architecture.

First, a type is defined to denote the values *on* and *off*. This type is to be the value of the interrupt status flag (the "interrupt flag").

$ONOFF == off \mid on$

The processor implements a finite number of interrupt types, each denoted by a small integer in the range *minintno* to *maxintno*.

$minintno, maxintno : \mathbb{N}$

minintno < maxintno

A type, *INTRPTNO* is defined to represent the interrupt number.

$INTRPTNO == minintno \dots maxintno$

The hardware state is represented by the following schema.

$\_HARDWARE \_$   $genregs : REGID \rightarrow WORD$  intflg : ONOFFintno : INTRPTNO

The hardware has a set of general-purpose registers, *genregs*, an interrupt flag, *intflg* and a number denoting the current interrupt (if there is one), *intno*. In a fuller model, *intno* would be used to activate the appropriate interrupt service routine. Here, it is used just to provide a parameter to the operation that raises software interrupts. The general-purpose registers, *genregs*, is a function from register identifier, *REGID*, to a value (represented as a single word).

First of all, we need operations to enable and disable interrupts. First, the operation to enable interrupts is defined.

Next, the operation that disables interrupts is defined.

Since these operations do not refer to the before state, their precondition is true.

The above operations merely operate on the interrupt flag in the simplified hardware models.

A Return From Interrupt instruction is assumed. On many processors, this operation corresponds to a single instruction, often called **rti**. Amongst other things, this operation disables interrupts, increments the program counter so that it points to the instruction after the one that caused the interrupt and restores it to the hardware so that execution can continue. Since much of this is internal to the processor, we only specify it in outline.

$ReturnFromInterrupt \cong$

... 8*EnableInts*

The process table, PTAB, is the structure maintained by the kernel to represent processes. Processes are represented as a collection of data items that collectively represent a process. As far as the hardware is concerned, it is necessary for each process' current stack top pointer to be stored in the process table. The reason for this is that, between activations, the values of the registers belonging to a process are stored on top of the stack.

```

PTAB \_ \\ \vdots \\ stacktop : PID \rightarrow ADDR \\ \vdots \\ dom stacktop = used \\ \vdots \\ \end{cases}

```

When a context switch occurs, the registers belonging to the outgoing process are pushed onto its stack. Then the registers of the incoming process are popped off its stack.

where *pushregs* is an operation that pushes all (necessary) registers onto the stack pointed to by *stacks(outpid?)* and *popregs* pops the equivalent registers from the stack pointed to by *stacks(inpid?)*. This is an old technique for storing registers; it has the enormous advantage that it does not require storage in the process table. It has another advantage: the registers are always in an easily accessible location and access to them is relatively cheap.

Because of the architecture of most processors, we are compelled to assume that there will always be sufficient space on the outgoing process' stack to hold all the necessary registers. This is, however, a matter for the programmer. Furthermore, nowhere is the size limit for the stack saved, so it is not possible to determine whether there is any space available; even if there were, the test might be too expensive to apply, so we are left where we began.

The precondition of *ContextSwitch* could be *true* or it could be

pre ContextSwitch  $\widehat{=}$  {inpid?, outpid?}  $\subseteq$  used

The process is only partially complete at this point. When the first process is executed, where do the outgoing registers come from? To solve this problem, we define the following operation

```

\begin{array}{c} --HalfContextSwitch \\ \hline \Delta HARDWARE \\ \hline \Xi PTAB \\ inproc?: PID \\ \hline \\ pushregszero(stacks(inproc?)) \end{array}

```